raw_format_nat_hex formats a natural to a hex string.str_trim returns a string from str'low to the first occurrence of NUL.str_replace replaces a string by a string.to_slv converts everything into a std_logic_vector in this case a integer to slv.log2ceilnz(x) calculates the needed bits to encode x symbols in binary.

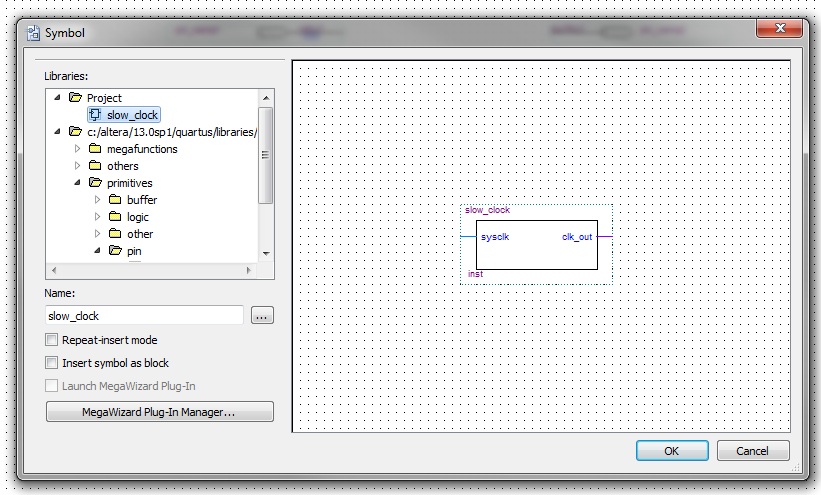

#Altera quartus ii create symbol code#

The last portion of code is a dummy constant in the entity, which calls the export function: CONSTANT test : boolean := dbg_ExportEncoding("OOBControl (Host)", dbg_GenerateEncodings, MY_PROJECT_DIR & "CSP/FSM_OOB_Host.tok") Write(l, str_trim(encodings(base to i-1))) Otherwise, the new parser of ISE 14.7 fails to slice properly. Write(l, "# Default token value") writeline(tokenFile, l) Write(l, "# ChipScope Token File Version") writeline(tokenFile, l) Write(l, "# Encoding file for '" & Name & "'") writeline(tokenFile, l) Report "dbg_ExportEncoding: '" & encodings & "'" severity note Report "Exporting encoding of '" & Name & "' to '" & tokenFileName & "'." severity note Global function - defined in : impure function dbg_ExportEncoding(Name : STRING encodings : string tokenFileName : STRING) return BOOLEAN isįile tokenFile : TEXT open WRITE_MODE is tokenFileName Return to_slv(T_STATE'pos(st), log2ceilnz(T_STATE'pos(T_STATE'high) + 1)) įunction dbg_GenerateEncodings return string is Local functions - per entity functions: function dbg_EncodeState(st : T_STATE) return STD_LOGIC_VECTOR is

The design uses 3 functions to export the FSM state encodings: Error (10657): VHDL Subprogram error at sata_PhysicalLayer.vhdl(514): failed to elaborate call to subprogram "dbg_ExportEncoding".Error (10346): VHDL error at debug.vhdl(47): formal port or parameter "encodings" must have actual or default value.Error (10351): VHDL Subprogram Body error at sata_PhysicalLayer.vhdl(504): function "dbg_GenerateEncodings" does not always return a value.My design can be synthesized with an alternative top-level as well for Altera FPGAs, but Quartus II seems to have a problem with return line.all. This functionality is tested with Xilinx ISE 14.7, iSim 14.7 and Mentor Graphic's QuestaSim 10.2c. I implemented some VHDL code to exports FSM state encodings at compile time, which can be read back by Xilinx ChipScope.

0 kommentar(er)

0 kommentar(er)